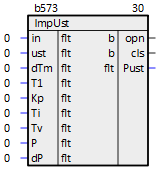

| Входы |

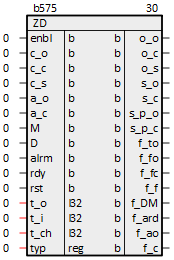

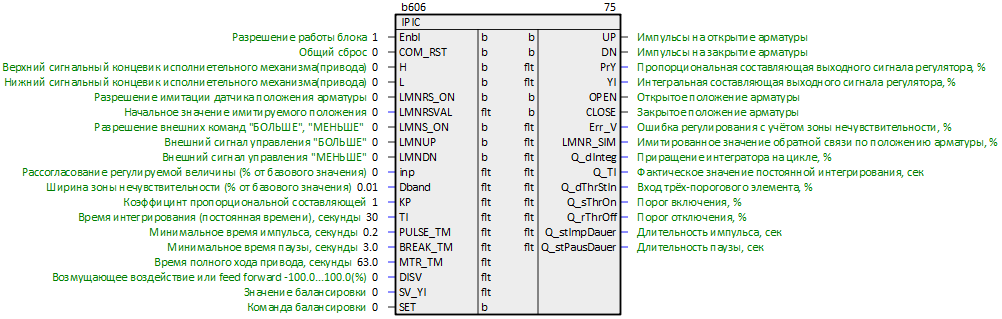

Enbl | Бит разрешения

работы блока |

COM_RST | Бит сброса

и перезагрузки регулятора |

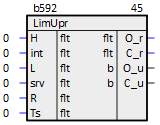

H | Сигнал верхнего

ограничения управляемого исполнительного элемента |

L | Сигнал нижнего

ограничения управляемого исполнительного элемента |

LMNRS_ON | Разрешение

имитации датчика положения управляемого исполнительного элемента |

LMNRSVAL | Начальное

значение имитируемого положения в % |

LMNS_ON | Разрешение

действия внешних команд «больше-меньше» |

LMNUP | Внешний

сигнал управления «больше» |

LMNDN | Внешний

сигнал управления «меньше» |

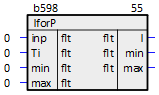

inp | Рассогласование

регулируемой величины в % от базового значения |

Dband | Ширина зоны

нечувствительности в % от базового значения |

KP | Коэффициент

пропорциональной составляющей |

TI | Постоянная

времени интегральной составляющей в секундах |

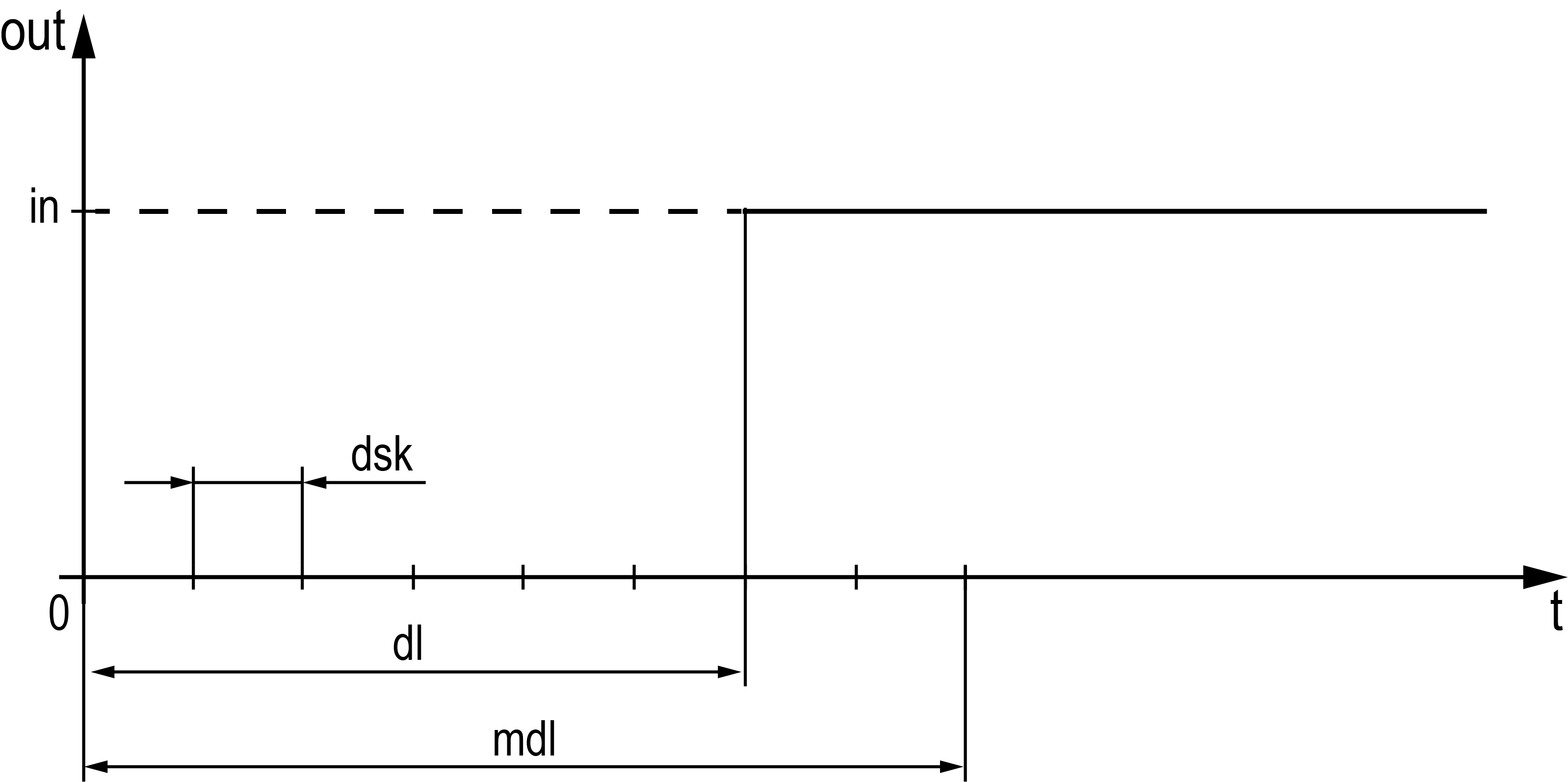

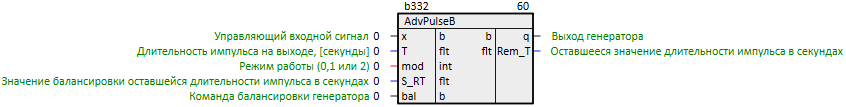

PULSE_TM | Минимальная

длительность импульса управления в секундах |

BREAK_TM | Минимальная

длительность паузы в секундах |

MTR_TM | Время полного

хода привода между крайними положениями в секундах |

DISV | Вход дополнительного

внешнего возмущающего воздействия: -100,0...100,0 % |

SV_YI | Значение

балансировки интегральной составляющей в % |

SET | Команда

балансировки интегральной составляющей |

| Выходы |

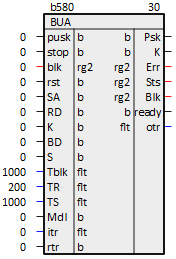

UP | Импульсы

на открытие управляемого элемента, инициализируется 0 |

DN | Импульсы

на закрытие управляемого элемента, инициализируется 0 |

PrY | Значение

пропорциональной составляющей выходного сигнала регулятора в %, инициализируется 0 |

YI | Значение

интегральной составляющей выходного сигнала регулятора в %, инициализируется 0 |

OPEN | Бит индикации

достижения открытого положения управляемого элемента, инициализируется 0 |

CLOSE | Бит индикации

достижения закрытого положения управляемого элемента, инициализируется 0 |

Err_V | Значение

ошибки регулирования с учетом зоны нечувствительности в %, инициализируется 0 |

LMNR_SIM | Имитированное

значение обратной связи по положению арматуры в % |

Q_dInteg | Приращение

интегратора за цикл в % |

Q_TI | Фактическое

значение постоянной интегрирования в секундах |

Q_dThrStIn | Значение

на входе трех-порогового элемента в % |

Q_sThrOn | Порог включения

в % |

Q_rThrOff | Порог отключения

в % |

Q_stImpDauer | Обратный

отсчет минимальной длительности импульса в секундах |

Q_stPausDauer | Обратный

отсчет минимальной длительности паузы в секундах |